具有宽占空比范围的40V同步降压直流/直流控制器

概要

CS5567E是具有宽占空比范围的40V同步降压控制器，旨在对高输入电压源或会发生高电压瞬变的输入电源轨进行电压调节，从而尽可能地减少对外部浪涌抑制组件的需求。高侧开关超短导通时间有助于获得较大的降压比，支持从40V标称输入到低电压轨的直接降压转换，从而降低系统的复杂性并减少解决方案成本。在输入电压突降至5.5V时，仍能根据需要以接近100%的占空比继续工作，因此非常适用于高性能工业控制、机器人、数据通信和射频应用。

CS5567E强制PWM模式运行，可以消除开关频率变化从而尽可能地降低EMI，而用户可选的轻载PSM模式则可以降低轻负载条件下的电流消耗。可调开关频率可同步至外部时钟源，从而消除噪声敏感应用中的拍频。

## 描述

- 宽输入电压范围：5.5V~40V

- 可调输出电压范围：0.8V~36V

- 40ns  $t_{ON(min)}$ , 可实现高V<sub>IN</sub>/V<sub>OUT</sub>比

- 140ns  $t_{OFF(min)}$ , 可实现低压降

- 开关频率范围为100KHz~1MHz

- 同步输入功能

- 可选轻载PSM模式或强制PWM模式

- 无损R<sub>DS(on)</sub>电感电流采样和限流

- $\pm 1\%$ 反馈精度的0.8V基准

- 具有迟滞功能的输入UVLO

- 具有迟滞功能的热关断保护

- 断续模式过流保护

应用

- 无线基础设施、云计算

- 电动自行车

- 非隔离式PoE、IP摄像头

- 工业电机驱动、测试和测量

- 资产跟踪和机群管理系统

- 反相降压/升压稳压器

封裝

- ## • EOA16

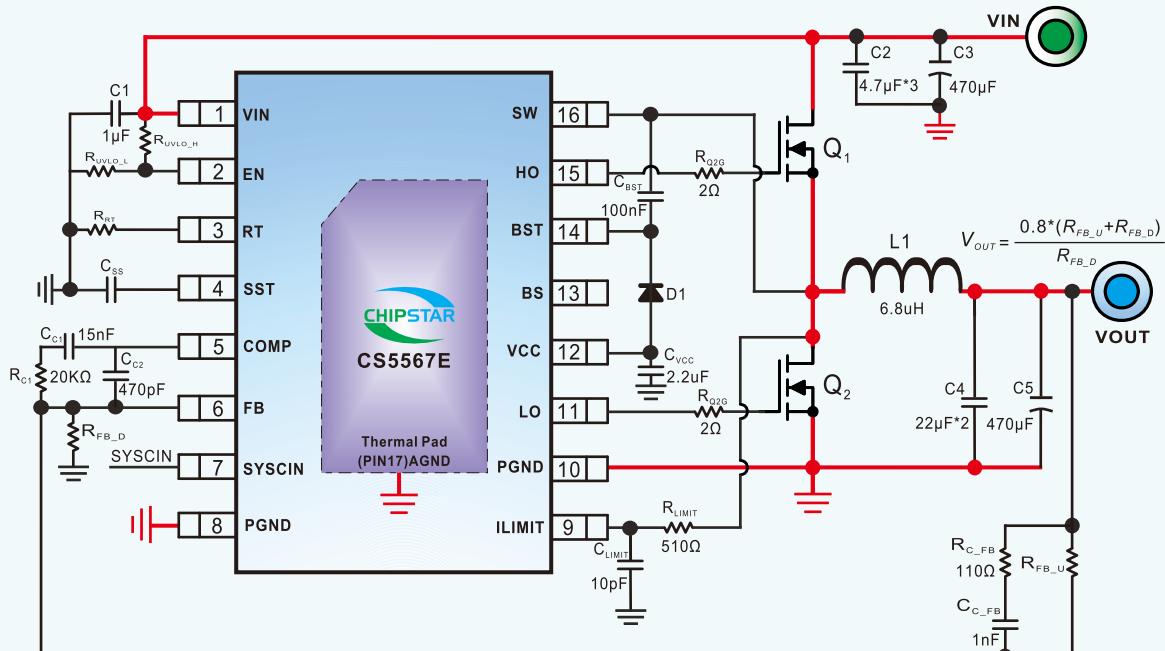

典型应用图

CS5567F 应用电路图

备注:

- 备注:**

(1) L1功率电感的饱和电流值须仔细进行确认，并留有足够的余量。

(2) 图中红色实线为流大电流路径。

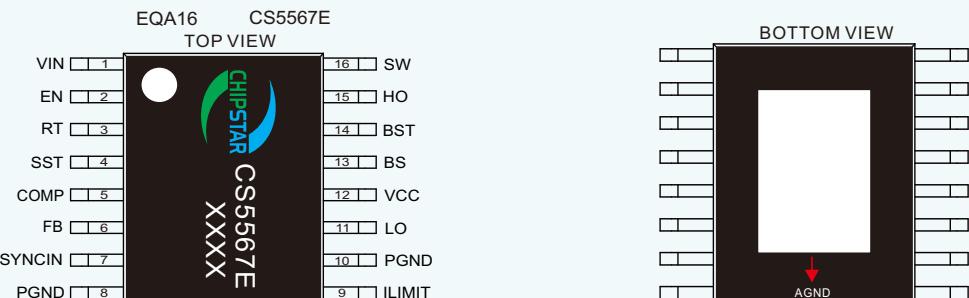

## 引脚排列以及定义

| 管脚编号 | 说明     | 输入/输出 | 功能                                                                       |

|------|--------|-------|--------------------------------------------------------------------------|

| 1    | VIN    | 电源    | 输入电源                                                                     |

| 2    | EN     | 输入    | 使能端                                                                      |

| 3    | RT     | 输入    | 振荡器频率设置管脚，内部振荡器通过 RT 和 AGND 之间的电阻编程                                      |

| 4    | SST    | 输入    | 软启动和电压跟踪引脚                                                               |

| 5    | COMP   | 输出    | 内部误差放大器的低阻抗输出，连接 COMP 引脚和 FB 引脚之间的环路补偿网络                                 |

| 6    | FB     | 输入    | 反馈连接至内部误差放大器的反向输入，从输出到该引脚的电阻分压设置输出电压电平                                   |

| 7    | SYNCIN | 输入    | 双功能引脚，提供可选的时钟输入。可设置轻载 PSM 或强制 PWM 模式，浮空或接地时选择轻载 PSM 模式，接 VCC 选择强制 PWM 模式 |

| 8    | PGND   | -     | 功率地                                                                      |

| 9    | ILIMIT | 输入    | 电流峰值调整管脚，电流采样比较器的输入                                                      |

| 10   | PGND   | -     | 功率地                                                                      |

| 11   | LO     | 输出    | 低压侧 MOSFET 栅极驱动输出                                                        |

| 12   | VCC    | 电源    | 内部 7.5V 偏置调节器的输出                                                         |

| 13   | BS     | 电源    | 内置二极管阴极端口，可以采用内置二极管，需将 BS 和 BST 短接。采用外置二极管时 BS 浮空                        |

| 14   | BST    | 电源    | 高侧栅驱动的自举电源                                                               |

| 15   | HO     | 输出    | 高侧 MOSFET 栅极驱动输出                                                         |

| 16   | SW     | 输入/输出 | 降压控制器的开关节点。                                                              |

| 17   | AGND   | -     | 模拟地                                                                      |

### 极限参数表<sup>1</sup>

| 参数               | 描述                          | 数值      | 单位 |

|------------------|-----------------------------|---------|----|

| INPUT            | VIN, EN                     | -0.3~55 | V  |

|                  | SW, ILIMIT                  | -1~55   | V  |

|                  | SW (20ns transient)         | -5~55   | V  |

|                  | VCC, SYNCIN                 | -0.3~14 | V  |

|                  | FB, COMP, SST, RT           | -0.3~6  | V  |

| OUTPUT           | BST                         | -0.3~65 | V  |

|                  | BST to VCC                  | ~55     | V  |

|                  | BST to SW, PGOOD            | -0.3~14 | V  |

|                  | VCC to BST (20ns transient) | 7       | V  |

|                  | LO (20ns transient)         | -3~     | V  |

| T <sub>J</sub>   | 结工作温度范围                     | -40~150 | °C |

| T <sub>STG</sub> | 存储温度范围                      | -55~150 | °C |

| T <sub>SDR</sub> | 引脚温度 (焊接 10s)               | 260     | °C |

### 推荐工作环境

| 参数             | 描述                     | 数值      | 单位 |

|----------------|------------------------|---------|----|

| INPUT          | VIN                    | 5.5~40  | V  |

|                | SW                     | -1~40   | V  |

|                | ILIMIT                 | 0~40    | V  |

|                | External VCC bias rail | 8~13    | V  |

|                | EN                     | -0.3~40 | V  |

| OUTPUT         | BST                    | -0.3~40 | V  |

|                | BST to VCC             | ~40     | V  |

|                | BST to SW              | 5~13    | V  |

|                | PGOOD                  | ~13     | V  |

| T <sub>J</sub> | 结工作温度范围                | -40~125 | °C |

| T <sub>A</sub> | 环境温度范围                 | -40~85  | °C |

### 热效应信息<sup>2</sup>

| 参数              | 描述           | 数值 | 单位   |

|-----------------|--------------|----|------|

| θ <sub>JA</sub> | 封装热阻-芯片到环境热阻 | 45 | °C/W |

### 订购信息

| 产品型号    | 封装形式  | 器件标示 | 包装尺寸 | 卷带宽度 | 数量         |

|---------|-------|------|------|------|------------|

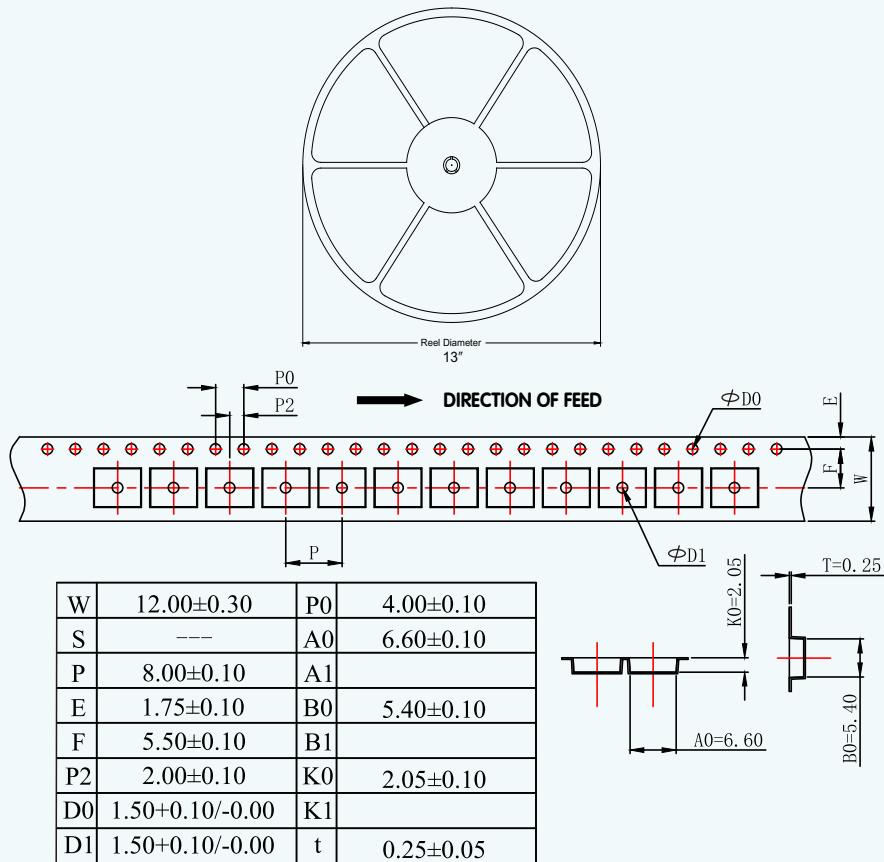

| IU5567E | EQA16 |      | 13"  | 12mm | 4000 units |

### ESD范围

HBM(人体静电模式) ----- ±2kV

MM( 机器静电模式) ----- ±200V

- 上述参数仅仅是器件工作的极限值，不建议器件的工作条件超过此极限值，否则会对器件的可靠性及寿命产生影响，甚至造成永久性损坏。

- PCB板放置CS5567E的地方，需要有散热设计，使得CS5567E底部的散热片和PCB板的散热区域相连。

上海智浦欣微电子有限公司

Chipstar Micro-electronics

CS5567E

**电气参数** ( $V_{VIN} = 24V$ ,  $V_{EN} = 1.5V$ ,  $T_J = 25^\circ C$ , unless otherwise stated)

| PARAMETER                               |                                             | TEST CONDITIONS                                                                                                   | MIN   | TYP  | MAX | UNIT             |

|-----------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|------|-----|------------------|

| <b>INPUT SUPPLY</b>                     |                                             |                                                                                                                   |       |      |     |                  |

| $V_{IN}$                                | Operating input voltage range               | $I_{VCC} \leq 10 \text{ mA at } V_{VIN} = 5.5 \text{ V}$                                                          | 5.5   | 40   |     | V                |

| $I_{Q-RUN}$                             | Operating input current, not switching      | $V_{EN} = 1.5 \text{ V}, V_{SST} = 0 \text{ V}$                                                                   |       | 1.5  |     | mA               |

| $I_{Q-STBY}$                            | Standby input current                       | $V_{EN} = 1 \text{ V}$                                                                                            |       | 1    |     | mA               |

| $I_{Q-SHDN}$                            | Shutdown input current                      | $V_{EN} = 0 \text{ V}, V_{VCC} < 1 \text{ V}$                                                                     |       | 5    |     | $\mu\text{A}$    |

| <b>VCC REGULATOR</b>                    |                                             |                                                                                                                   |       |      |     |                  |

| $V_{VCC}$                               | VCC regulation voltage                      | $V_{SST} = 0 \text{ V}, 9 \text{ V} \leq V_{VIN} \leq 40 \text{ V}, 0 \text{ mA} \leq I_{VCC} \leq 20 \text{ mA}$ | 7.5   |      |     | V                |

| $V_{VCC-LDO}$                           | VIN to VCC dropout voltage                  | $V_{VIN} = 6 \text{ V}, V_{SS/TRK} = 0 \text{ V}, I_{VCC} = 20 \text{ mA}$                                        | 0.25  | 0.72 |     | V                |

| $I_{SC-LDO}$                            | VCC short-circuit current                   | $V_{SST} = 0 \text{ V}, V_{VCC} = 0 \text{ V}$                                                                    | 100   |      |     | mA               |

| $V_{VCC-UV}$                            | VCC undervoltage threshold                  | $V_{VCC}$ rising                                                                                                  | 4.8   | 4.93 | 5.2 | V                |

| $V_{VCC-UVH}$                           | VCC undervoltage hysteresis                 | Rising threshold – falling threshold                                                                              | 0.26  |      |     | V                |

| $V_{VCC-EXT}$                           | Minimum external bias voltage               | Voltage required to disable VCC regulator                                                                         | 8     |      |     | V                |

| $I_{VCC}$                               | External VCC input current, not switching   | $V_{SST} = 0 \text{ V}, V_{VCC} = 13 \text{ V}$                                                                   |       | 1.2  |     | mA               |

| <b>ENABLE AND INPUT UVLO</b>            |                                             |                                                                                                                   |       |      |     |                  |

| $V_{SHDN}$                              | Shutdown to standby threshold               | $V_{EN}$ rising                                                                                                   | 0.405 |      |     | V                |

| $V_{EN}$                                | Standby to operating threshold              | $V_{EN}$ rising                                                                                                   | 1.2   |      |     | V                |

| $I_{EN-HYS}$                            | Standby to operating hysteresis current     | $V_{EN} = 1.5 \text{ V}$                                                                                          | 9     | 10   | 11  | $\mu\text{A}$    |

| <b>ERROR AMPLIFIER</b>                  |                                             |                                                                                                                   |       |      |     |                  |

| $V_{REF}$                               | FB reference Voltage                        | FB connected to COMP                                                                                              | 800   |      |     | mV               |

| $I_{FB-BIAS1}$                          | FB input bias current                       | $V_{FB} = 0.8 \text{ V}, -40^\circ C \leq T_J \leq 125^\circ C$                                                   | -0.1  | 0.1  |     | $\mu\text{A}$    |

| $I_{FB-BIAS2}$                          | FB input bias current                       | $V_{FB} = 0.8 \text{ V}, -40^\circ C \leq T_J \leq 150^\circ C$                                                   | -0.2  | 0.2  |     | $\mu\text{A}$    |

| $V_{COMP-HI}$                           | COMP output high voltage                    | $V_{FB} = 0 \text{ V}, \text{COMP sourcing } 1 \text{ mA}$                                                        | 5     |      |     | V                |

| $V_{COMP-LO}$                           | COMP output low voltage                     | COMP sinking 1 mA                                                                                                 |       | 0.3  |     | V                |

| AVOL                                    | DC gain                                     |                                                                                                                   | 94    |      |     | dB               |

| GBW                                     | Unity gain bandwidth                        |                                                                                                                   | 4     |      |     | MHz              |

| <b>SOFT-START and VOLTAGE TRACKING</b>  |                                             |                                                                                                                   |       |      |     |                  |

| $I_{SS}$                                | SST capacitor charging current              | $V_{SST} = 0 \text{ V}$                                                                                           | 10    |      |     | $\mu\text{A}$    |

| $R_{SS}$                                | SST discharge FET resistance                | $V_{EN} = 1 \text{ V}, V_{SST} = 0.1 \text{ V}$                                                                   | 11    |      |     | $\Omega$         |

| <b>OSCILLATOR</b>                       |                                             |                                                                                                                   |       |      |     |                  |

| $F_{SW1}$                               | Oscillator frequency – 1                    | $R_{RT} = 100 \text{ k}\Omega$                                                                                    | 100   |      |     | kHz              |

| $F_{SW2}$                               | Oscillator frequency – 2                    | $R_{RT} = 25 \text{ k}\Omega$                                                                                     | 380   | 400  | 420 | kHz              |

| $F_{SW3}$                               | Oscillator frequency – 3                    | $R_{RT} = 12.5 \text{ k}\Omega$                                                                                   | 780   |      |     | kHz              |

| <b>SYNCHRONIZATION INPUT AND OUTPUT</b> |                                             |                                                                                                                   |       |      |     |                  |

| $F_{SYNC}$                              | SYNCIN external clock frequency range       | % of nominal frequency set by $R_{RT}$                                                                            | -20%  | 50%  |     |                  |

| $V_{SYNC-HI}$                           | SYNCIN input logic high                     |                                                                                                                   | 2     |      |     | V                |

| $V_{SYNC-LI}$                           | SYNCIN input logic low                      |                                                                                                                   |       | 0.8  |     | V                |

| $R_{SYNC-IN}$                           | SYNCIN input resistance                     | $V_{SYNCIN} = 3 \text{ V}$                                                                                        | 19    |      |     | $\text{k}\Omega$ |

| $T_{SYNCI-PW}$                          | SYNCIN input minimum pulselwidth            | Minimum high state or low state duration                                                                          | 50    |      |     | ns               |

| $T_{SYNCIN}$                            | Delay from SYNCIN rising to HO leading edge | 50% to 50%                                                                                                        | 120   |      |     | ns               |

| <b>GATE DRIVERS</b>                     |                                             |                                                                                                                   |       |      |     |                  |

| $R_{HO-UP}$                             | HO high state resistance, HO to BST         | $V_{BST} - V_{SW} = 7 \text{ V}, I_{HO} = -100 \text{ mA}$                                                        | 2.2   |      |     | $\Omega$         |

| $R_{HO-DOWN}$                           | HO low state resistance, HO to SW           | $V_{BST} - V_{SW} = 7 \text{ V}, I_{HO} = 100 \text{ mA}$                                                         | 1.3   |      |     | $\Omega$         |

| $R_{LO-UP}$                             | LO high state resistance, LO to VCC         | $V_{BST} - V_{SW} = 7 \text{ V}, I_{LO} = -100 \text{ mA}$                                                        | 2.3   |      |     | $\Omega$         |

| $R_{LO-DOWN}$                           | LO low state resistance, LO to PGND         | $V_{BST} - V_{SW} = 7 \text{ V}, I_{LO} = 100 \text{ mA}$                                                         | 1.3   |      |     | $\Omega$         |

上海智浦欣微电子有限公司

Chipstar Micro-electronics

CS5567E

| PARAMETER                                                   | TEST CONDITIONS                              | MIN                                                             | TYP  | MAX | UNIT            |

|-------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|------|-----|-----------------|

| <b>BOOTSTRAP DIODE AND UNDERVOLTAGE THRESHOLD</b>           |                                              |                                                                 |      |     |                 |

| $V_{BST-UV}$                                                | BST to SW undervoltage detection             | $V_{BST} - V_{SW}$ falling                                      |      | 3.4 | V               |

| $V_{BST-HYS}$                                               | BST to SW undervoltage hysteresis            | $V_{BST} - V_{SW}$ rising                                       |      | 0.3 | V               |

| <b>PWM CONTROL</b>                                          |                                              |                                                                 |      |     |                 |

| $t_{ON(min)}$                                               | Minimum controllable on-time                 | $V_{BST} - V_{SW} = 7$ V, HO 50% to 50%                         | 40   | 60  | ns              |

| $t_{OFF(min)}$                                              | Minimum off-time                             | $V_{BST} - V_{SW} = 7$ V, HO 50% to 50%                         | 140  | 200 | ns              |

| $V_{RAMP(min)}$                                             | RAMP valley voltage (COMP at 0% duty cycle)  |                                                                 | 300  |     | mV              |

| $k_{FF}$                                                    | PWM feedforward gain ( $V_{IN} / V_{RAMP}$ ) | $6 \leq V_{VIN} \leq 40$ V                                      | 15   |     | V/V             |

| <b>OVER CURRENT PROTECT (OCP) – VALLEY CURRENT LIMITING</b> |                                              |                                                                 |      |     |                 |

| $I_{RS}$                                                    | ILIMT source current, $R_{SENSE}$ mode       | Low voltage detected at ILIMT                                   | 90   | 100 | 110             |

| $I_{RDS(ON)}$                                               | ILIMT source current, $R_{DS-ON}$ mode       | SW voltage detected at ILIMT, $T_j = 25^\circ C$                | 180  | 200 | 220             |

| $I_{RDS(ON)TC}$                                             | ILIMT current tempco                         | $R_{DS-ON}$ mode                                                | 4500 |     | ppm/ $^\circ C$ |

| $I_{RTC}$                                                   | ILIMT current tempco                         | $R_{SENSE}$ mode                                                | 0    |     | ppm/ $^\circ C$ |

| $V_{ILIM-TH}$                                               | ILIMT comparator threshold at ILIMT          |                                                                 | -8   | -2  | 3.5             |

| <b>HICCUP MODE FAULT PROTECTION</b>                         |                                              |                                                                 |      |     |                 |

| $C_{HICC-DEL}$                                              | Hiccup mode activation delay                 | Clock cycles with current limiting before off-time activated    | 128  |     | cycles          |

| $C_{HICCUP}$                                                | Hiccup mode off time after activation        | Clock cycles with no switching followed by SST release          | 8192 |     | cycles          |

| <b>DIODE EMULATION / DCM OPERATION</b>                      |                                              |                                                                 |      |     |                 |

| $V_{ZCD-SS}$                                                | Zero-cross detect (ZCD) soft-start ramp      | ZCD threshold measured at SW pin 50 cycles after first HO pulse | 0    |     | mV              |

| $V_{DEM-TH}$                                                | Diode emulation zero-cross threshold         | Measured at SW with $V_{SW}$ rising                             | -5   | 0   | 5               |

| <b>THERMAL SHUTDOWN</b>                                     |                                              |                                                                 |      |     |                 |

| $T_{SD}$                                                    | Thermal shutdown threshold                   | $T_j$ rising                                                    | 175  |     | $^\circ C$      |

| $T_{SD-HYS}$                                                | Thermal shutdown hysteresis                  |                                                                 | 20   |     | $^\circ C$      |

| <b>SWITCHING CHARACTERISTICS</b>                            |                                              |                                                                 |      |     |                 |

| $T_{HO-TR}, T_{LO-TR}$                                      | HO, LO rise times                            | $V_{BST} - V_{SW} = 7$ V, $C_{LOAD} = 1nF$ , 20% to 80%         | 15   |     | ns              |

| $T_{HO-TF}, T_{LO-TF}$                                      | HO, LO fall times                            | $V_{BST} - V_{SW} = 7$ V, $C_{LOAD} = 1nF$ , 20% to 80%         | 15   |     | ns              |

| $T_{HO-DT}$                                                 | HO turn-on dead times                        | $V_{BST} - V_{SW} = 7$ V, LO off to HO on, 50% to 50%           | 100  |     | ns              |

| $T_{LO-DT}$                                                 | LO turn-on dead times                        | $V_{BST} - V_{SW} = 7$ V, HO off to LO on, 50% to 50%           | 100  |     | ns              |

## CS5567E应用要点

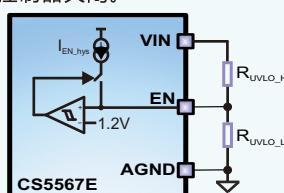

### 1. Enable (UVLO设置)

EN输入支持可调输入欠压锁定 ( UVLO )，滞回电压由电阻编程，以满足特定应用的通电和断电要求：

阶段一：当 $V_{EN} < V_{EN\_L}$ ，控制器处于关闭模式；

阶段二：当 $1V < V_{EN} < 1.2V$ ，控制器处于待机模式，VCC调节器工作，SST引脚接地，HO和LO输出无开关；

阶段三：当 $V_{EN} > 1.2V$ ，脉冲宽度调制的栅极驱动信号被传送到HO和LO引脚，此时控制器处于正常工作模式， $I_{EN\_hys}$ 电流源启用并流经外部UVLO分压电阻以提供滞回电压；

阶段四：当 $V_{EN}$ 从待机模式或正常工作模式下降到 $V_{EN} < 0.4V$ 时，控制器关闭。

$$R_{UVLO\_H} = \frac{V_{START} - V_{STOP}}{I_{EN\_hys}}$$

$$R_{UVLO\_L} = \frac{V_{EN} \cdot R_{UVLO\_H}}{V_{START} - V_{EN}}$$

上式中：

- $V_{START}$ 是预设的VIN管脚开启电压；

- $V_{STOP}$ 是预设的VIN管脚关闭电压；

- $V_{EN}$ 是EN管脚使能开启电压，1.2V@TYP；

- $I_{EN\_hys}$ 是EN管脚内置迟滞电流，10uA@TYP；

### 2. 开关频率设置

CS5567E的开关频率 $F_{sw}$ 有两种设置选项，这为各种应用选择外部组件时提供了一定程度的灵活性。要调整频率，可以在RT引脚和AGND之间使用一个电阻，或者通过SYNCIN引脚将芯片与外部时钟信号同步。

在RT引脚与AGND之间接入一个电阻，可以调整自由运行的开关频率。开关频率范围为100KHz至1MHz。频率设置电阻 $R_{RT}$ 由下面公式决定：

$$R_{RT}(K\Omega) = \frac{10000}{F_{sw}(KHz)}$$

向CS5567E施加外部时钟同步信号，以同步频率和相位的切换。外部时钟SYNC信号的要求是：

- 时钟频率范围：100KHz~1MHz；

- 时钟频率： $R_{RT}$ 设置的自由运行频率的20%~+50%；

- 时钟最大电压幅度：13V；

- 时钟最小脉冲宽度：50ns；

### 3. 软启动设置

当EN引脚超过其1.2V的上升阈值后，CS5567E开始将输出充电至反馈电阻网络规定的直流电平。CS5567E具有可调软启动功能（由SST引脚到GND的电容设置），可确定输出的充电时间。一个10 $\mu$ A的电流源为这个软启动电容器充电。软启动限制了高输出电容导致的涌入电流，以避免过电流情况。输入电源轨上的应力也减小了。软启动时间 $t_{ss}$ 由下式设置：

$$C_{ss}(nF) = \frac{I_{ss} \cdot t_{ss}(ms)}{V_{REF}} = \frac{10\mu A \cdot t_{ss}(ms)}{0.8V} = 12.5 \cdot t_{ss}(ms)$$

SST引脚内部箝位到 $V_{FB} + 115mV$ ，以允许从过载情况下软启动恢复。箝位电路需要大于2nF的软启动电容才能稳定，电流限制约为2mA。

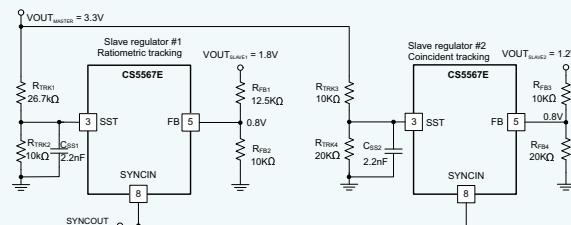

### 4. SST跟踪功能

当需要主从电源跟踪时，SST引脚还兼作跟踪引脚。这种跟踪是通过简单的电阻网络对主设备的输出电压进行分压来实现的。重合、比率和偏移跟踪模式都是可能的。如果外部电压源连接到SST引脚，则芯片外部软启动能力将被有效禁用。当SST引脚达到0.8V参考电压电平时，达到调节的输出电压电平。确定是否需要外部软启动电容，来防止设备在启动期间进入电流限制。同样，如果启用了跟踪功能，必须注意到输入电源的斜坡速度有多快。

最常见的应用是重合跟踪，用于DSP和FPGA实现中的内核与I/O电压跟踪。重合跟踪强制主通道和从通道具有相同的输出电压斜率，直到从通道输出达到其调节设定点。相反，比例跟踪将从机的输出电压设置为启动期间主机输出电压的一小部分。比例和重合两种实用跟踪配置如下图所示：

对于重合跟踪，将从稳压器的SST输入从主稳压器的输出电压连接到电阻分压，该分压与从稳压器FB引脚上使用的分压器相同，即 $R_{TRK1}=R_{FB3}$ 和 $R_{TRK4}=R_{FB4}$ 。当主电压升高时，从电压同样升高（除了 $V_{FB}$ 低于0.8V时从SST到FB的80mV偏移）。最终从机电压达到其调节电压，此时内部基准接管调节，而SST输入继续高于FB 115mV，并且不再控制输出电压。

在所有情况下，为了确保输出电压精度不会因SST电压太接近0.8V参考电压而受到影响，从机的SST电压的最终值应至少比FB高100mV。

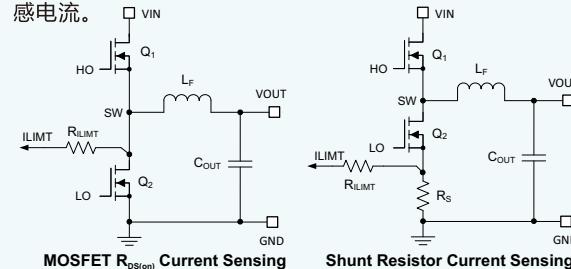

### 5. 电流检测与过流保护 (ILIMIT)

CS5567E实现了一种无损电流检测方案，用于在过载或短路条件下限制电感电流。

下图左侧是常用的低侧MOSFET的on-state电阻 $R_{DS(on)}$ 电流感测方法，右侧是具有电流分流电阻 $R_s$ 的替代方案。

CS5567E在芯片PWM关闭时间（LO为高时）期间检测电感电流。

CS5567E的ILIMIT引脚提供流入外部电阻（指定为 $R_{ILIMIT}$ ）的参考电流，以编程电流限制阈值。如果ILIMIT引脚电压低于GND，则ILIMIT脚上的电流限制比较器防止进一步的SW脉冲。芯片在启动时检测适当的模式，并相应地设置源电流振幅和温度系数（TC）。具有 $R_{DS(on)Q2}$ 感测的ILIMIT电流在27°C结温下为200μA，并包含+4500ppm/°C的TC，以通常跟踪低侧MOSFET的 $R_{DS(on)}$ 温度变化。相反，在RSENSE模式下，ILIMIT电流是恒定的100μA。这控制了稳态期间感应器电流的谷值输出过载。

根据所选模式，使用下式选择 $R_{ILIMIT}$ 的电阻：

$$R_{ILIMIT} = \frac{I_{OUT} - \Delta I_L / 2}{I_{RDSON}} * R_{DS(on)Q2} \quad R_{DS(on)} \text{ sensing}$$

$$R_{ILIMIT} = \frac{I_{OUT} - \Delta I_L / 2}{I_{RS}} * R_s \quad \text{shunt sensing}$$

- $\Delta I_L$ 是峰峰值电感纹波电流；

- $R_{DS(on)Q2}$ 是低侧MOSFET的导通电阻；

- $I_{RDSON}$ 是 $R_{DS-ON}$ 模式下的ILIMIT引脚电流；

- $R_s$ 是电流传感分流元件的电阻；

- $I_{RS}$ 是 $R_{SENSE}$ 模式下的ILIMIT引脚电流；

由于ILIMIT在 $R_{DS(on)}$ 感测模式下的电压波动较大，从ILIMIT连接到PGND的 $C_{ILIMIT}$ 电容对于谷值电流限制电路的运行很重要。选择电容使时间常数 $R_{ILIMIT} * C_{ILIMIT}$ 约为6ns。请注意，使用分流组件的电流感测通常在较低的输出电流水平下实现，以提供准确的过流保护。由于不可避免的效率损失、PCB布局和额外的成本影响，这种配置通常不会在高电流应用中实现（除非OCP设定点精度和工作温度范围内的稳定性是关键规格）。

## 6. 轻载PSM模式与强制PWM模式选择

CS5567E提供轻载PSM与强制PWM两种模式供用户选择，通过SYNCIN引脚的电压设置来实现。

当SYNCIN引脚连接到AGND或保持浮空时，CS5567E选择轻载PSM模式，在轻载PSM模式下，通过过零比较器感测SW电压来检测反向电流，当检测到轻载时出现反向电流后，低侧MOSFET被关闭。这种配置的好处是在空载和轻载条件下降低功率损耗，缺点是轻载瞬态响应较慢。

当SYNCIN引脚连接到VCC上时，CS5567E工作在强制PWM连续导通模式（CCM）。

## 7. 热关断

CS5567E内置有结温监测器。若温度超过过温值，则会发生热关断。当进入热关断状态时：

- 关闭高侧和低侧的MOSFET；

- 将SST拉低；

- 关闭VCC稳压器；

- 当芯片温度下降至热关断滞回温度时，启动软启动序列。这是一种非闭锁保护，如果故障持续存在，设备将反复进入和退出热关机状态；

## 8. Power MOSFETs

功率MOSFET的选择对DC/DC稳压器的性能有重大影响。具有低导通状态电阻 $R_{DS(on)}$ 的MOSFET降低了传导损耗，而低寄生电容使转换时间更快，开关损耗更低。通常，MOSFET的 $R_{DS(on)}$ 越低，栅极电荷 $Q_g$ 和输出电荷 $Q_{oss}$ 越高，反之亦然。因此，产品 $R_{DS(on)} * Q_g$ 通常指定为MOSFET优值。低热阻确保MOSFET的功耗不会导致

MOSFET芯片温度过高。在CS5567E应用中影响功率MOSFET选择的主要参数如下：

- $V_{GS} = 7.5V$ 时 $R_{DS(on)}$ ；

- 漏源额定电压 $BV_{DSS}$ ；

- $V_{GS} = 7.5V$ 时的栅极充电参数；

- 相关输入电压下的输出电荷 $Q_{oss}$ ；

- 体二极管反向恢复充电 $Q_{RR}$ ；

- 栅极阈值电压 $V_{GS(th)}$ ；

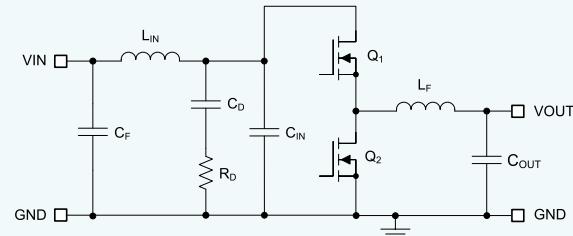

## 9. EMI Filter Design

开关稳压器具有负输入阻抗，在最小输入电压下最低。欠阻尼LC滤波器在滤波器的谐振频率处表现出高输出阻抗。为了稳定，滤波器输出阻抗必须小于转换器输入阻抗的绝对值。

EMI滤波器设计步骤如下：

- 计算开关频率下EMI滤波器的所需衰减，其中 $C_{IN}$ 表示开关转换器输入处的现有电容；

- 输入滤波器电感 $L_{IN}$ 通常在1μH和10μH之间选择，但它可以更低，以减少大电流设计中的损耗；

- 计算输入滤波电容 $C_F$ ；

通过从输入电流波形的傅里叶级数计算一次谐波电流，并将其乘以输入阻抗（阻抗由现有输入电容器 $C_{IN}$ 定义），导出了一个公式，以获得所需的衰减，如下式所示：

$$Attn = 20\log\left(\frac{I_{L(Peak)}}{\pi^2 * F_{SW} * C_{IN}} * \sin(\pi * D_{MAX}) * \frac{1}{1\mu V}\right) - V_{MAX}$$

- $V_{MAX}$ 是适用EMI标准的噪声规格，单位为dBμV，例如CISPR 32 Class B；

- $D_{MAX}$ 是最大占空比；

- $I_{PEAK}$ 是峰值电感电流；

出于滤波器设计的目的，输入处的电流可以建模为方波。EMI滤波器电容 $C_F$ 根据下式确定：

$$C_F = \frac{1}{L_{IN}} \left( \frac{10}{2\pi * F_{SW}} \right)^2$$

将输入滤波器添加到开关调节器中可以修改控制到输出的传递函数。滤波器的输出阻抗必须足够小，以便输入滤波器不会显著影响Buck转换器的环路增益。阻抗在滤波器谐振频率处达到峰值。滤波器的谐振频率由下式给出：

$$f_{res} = \frac{1}{2\pi * (L_{IN} * C_F)^{0.5}}$$

$R_D$ 的目的是降低滤波器在谐振频率下的峰值输出阻抗。电容 $C_D$ 阻止输入电压的DC分量，以避免 $R_D$ 中的过度功耗。电容 $C_D$ 在谐振频率下的阻抗必须低于 $R_D$ ，电容值大于输入的电容值 $C_{IN}$ 。这可以防止 $C_{IN}$ 干扰主滤波器的截止频率。当滤波器的输出阻抗在谐振频率处较高时（ $L_{IN}$ 和 $C_{IN}$ 形成的滤波器的Q过高），需要增加阻尼。电解电容 $C_D$ 可用于阻尼，其值由下式给出：

$$C_D \geq 4 * C_{IN}$$

使用下式选择阻尼电阻 $R_D$ :

$$R_D = (L_{IN} / C_{IN})^{0.5}$$

## 11. Power Supply Recommendations

CS5567E降压控制器设计为在5.5V~40V的宽输入电压范围内工作。输入电源的特性必须与绝对最大额定值和建议的工作条件兼容。此外，输入电源必须能够向满载调节器提供所需的输入电流。

如果转换器通过长线或阻抗较大的PCB走线连接到输入电源，请特别注意实现稳定的性能。输入电缆的寄生电感和电阻可能会对转换器的运行产生不利影响。寄生电感与低

ESR陶瓷输入电容器结合，形成了一个欠阻尼谐振电路。每次输入电源开启和关闭时，该电路都可能在VIN处产生瞬态过电压。寄生电阻会导致负载瞬变时输入电压下降。如果芯片在接近最小输入电压的情况下工作，这种下降可能会导致错误的UVLO故障触发和系统复位。解决这些问题的最佳方法是缩短输入电源到芯片的距离，并在陶瓷电容器上并联一个铝或钽输入电容。电解电容的中等有效串联电阻(ESR)有助于阻尼输入谐振电路，并减少任何电压过冲。通常，电容值在10μF~47μF之间就足以提供输入阻尼，并有助于在大负载瞬变期间保持输入电压稳定。EMI输入滤波器通常被置于芯片之前，除非经过精心设计，否则可能会导致系统不稳定，并产生上述一些影响。

## Layout Guidelines

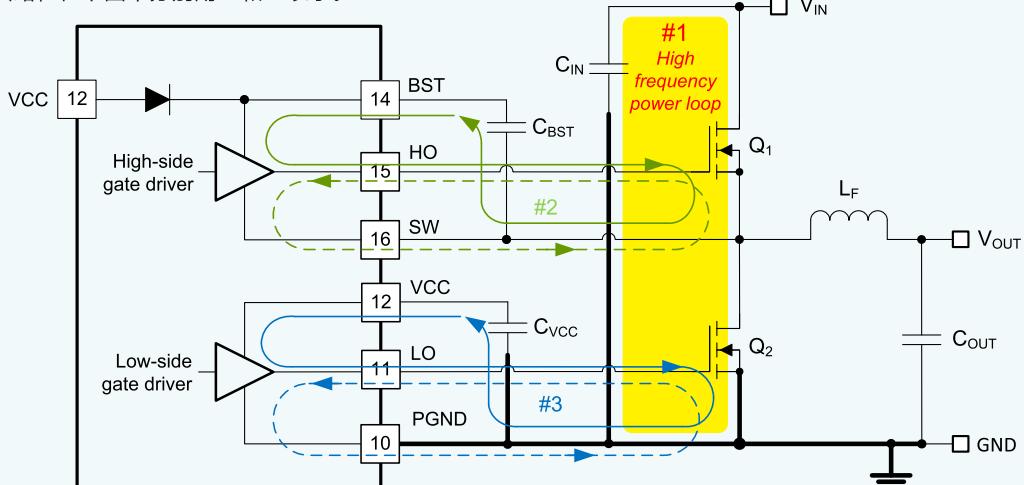

适当的PCB设计和布局在大电流、快速开关电路中非常重要，以确保适当的设备操作和设计鲁棒性。Buck的高频功率环在下图的黄色阴影区域中，转换器功率级由#1表示。Buck变换器的拓扑结构意味着特别高的di/dt电流在回路#1的元件中流动，并且必须通过最小化其有效回路面积来降低该回路的寄生电感。同样重要的是低侧和高侧MOSFET的栅极驱动回路，在下图中分别用#2和#3表示。

DC/DC Regulator Ground System With Power Stage and Gate Drive Circuit Switching Loops

### 1. Power Stage Layout

(1) 输入电容、输出电容和MOSFET是降压调节器的功率级的组成部件，通常放置在PCB的顶部(solder side)。由于利用任何系统级气流，对流传热的优势最大。在双面PCB布局中，小信号分量通常放在底侧(component side)。插入至少一个连接到地的内部平面，以屏蔽小信号走线并将其与噪声功率走线和线路隔离。

(2) DC/DC转换器具有多个大电流回路。最小化这些回路的面积，以抑制产生的开关噪声和寄生回路电感，并优化开关性能。

- 回路#1：将面积最小化的最重要回路是从输入电容通过高侧和低侧MOSFET，并通过接地连接回到电容的路径。将输入电容负端连接到靠近低侧MOSFET源极的位置(接地)。同样，将输入电容正端连接到靠近高侧MOSFET漏极的位置(VIN处)；

- 另一个回路，虽然不如回路#1重要，是从低侧MOSFET通过电感和输出电容，再通过地回到低侧MOSFET源极的路径。将低侧MOSFET的源极和输出电容的负端尽可能靠近地连接；

(3) 定义为SW节点的PCB走线，连接到高侧MOSFET的源极、低侧MOSFET的漏极和电感的高压侧，必须短而宽。然而，SW连接是注入EMI的来源，因此面积不能太大。

(4) 遵循MOSFET制造商推荐的MOSFET布局考虑因素，包括焊盘几何形状和焊膏模板设计。

(5) SW引脚连接到功率转换级的开关节点，并充当高侧栅极驱动器的返回路径。回路#1固有的寄生电感和两个功率MOSFET的输出电容( $C_{oss}$ )形成了一个谐振电路，在SW节点上感应出高频(>100MHz)振铃。如果不加以控制，这种振铃的电压峰值可能会明显高于输入电压。确保峰值振铃幅度不超过SW引脚的绝对最大额定限值。在许多情况下，从SW节点连接到GND的串联电阻器和电容器吸波网络会抑制振铃并降低峰值振幅。在PCB布局中为吸波网络组件提供工位。如果测试显示SW引脚处的振铃幅度过大，则根据需要采用吸波网络组件。

(6) 在高侧MOSFET导通时，一个脉冲电流从VIN流向低侧MOSFET的二极管，以恢复空间区域中的大部分栅极电荷，这就是二极管从正向偏置到反向恢复操作的Qrr。这个脉冲电流水平可能远高于负载电流：栅极电荷量取决于二极管的PN结，而峰值电流仅受寄生电容的限制。当二极管反向偏置时，SW节点上升高侧电流变为电感电流。

## 2. Gate Drive Layout

CS5567E高侧和低侧栅极驱动器能够以非常快的上升和下降时间提供大的峰值电流，以促进功率MOSFET的快速导通和关断转换。如果走线长度和阻抗没有得到很好的控制，非常高的di/dt会导致不可接受的振铃。

最小化杂散或寄生栅极回路电感是优化栅极驱动开关性能的关键，无论是与MOSFET栅极电容谐振的串联栅极电感，还是提供与栅极驱动命令相反的负反馈分量的共源极电感（栅极和电源回路共有），都会增加MOSFET开关时间。以下回路很重要：

- 回路#2：高侧MOSFET，Q1。在高侧MOSFET导通期间，大电流从自举电容流过栅极驱动器和高侧MOSFET，并通过SW连接流回自举电容的负端。相反，为了关断高侧MOSFET，大电流从高侧MOSFET的栅极流过栅极驱动器和SW，并通过SW走线流回高侧MOSFET；

- 回路#3：低侧MOSFET，Q2。在低侧MOSFET导通期间，大电流从VCC去耦电容流过栅极驱动器和低侧MOSFET，并通过地流回电容的负端。相反，为了关断低侧MOSFET，大电流从低侧MOSFET的栅极流过栅极驱动器和GND，并通过地流回低侧MOSFET；

强烈建议在设计高速MOSFET栅极驱动电路时遵循以下电路布局指南：

( 1 ) 从栅极驱动器输出HO和LO到高侧或低侧MOSFET的相应栅极的连接必须尽可能短，以减少串联寄生电感。使用0.65mm ( 25mils ) 或更宽的走线。如有必要，沿这些走线使用直径至少为0.5mm ( 20mils ) 的一个或多个过孔。利用磁通抵消，将HO和SW栅极走线作为差分对从芯片布线到高侧MOSFET。

( 2 ) 最小化VCC和BST引脚通过其各自电容的电流环路路径，因为它们提供的瞬态大电流对MOSFET栅极电容充电。将自举电容C<sub>BST</sub>布置在靠近芯片的BST和SW引脚的位置，以最小化与高侧驱动器相关联的回路#2的面积。类似地，将VCC电容C<sub>VCC</sub>布置在芯片的VCC和PGND引脚附近，以最小化与低侧驱动器相关联的回路#3的面积。

( 3 ) 可将2Ω~10Ω电阻与自举电容串联放置，减缓高侧MOSFET开启变化，以增加MOSFET的导通功率损耗为代价，用于减少SW节点处的电压振铃和峰值幅度。

## 3. PWM Controller Layout

为了使控制器尽可能靠近MOSFET以最小化栅极驱动器走线，以下考虑了与模拟和反馈信号、电流限制设置和温度感测相关的组件：

- ( 1 ) 分离电源和信号走线，并使用接地平面提供噪声屏蔽。

- ( 2 ) 将所有敏感的模拟信号走线和组件（如COMP、FB、RT、ILIMIT和SST）远离SW、HO、LO或BST等高压开关节点，以避免相互耦合。将一个或多个内部图层用作接地平面。特别注意屏蔽从电源走线及元件的反馈（FB）走线。

- ( 3 ) 上反馈电阻可以直接连接到负载设备处的输出电压感测点或转换器侧的大容量电容。

- ( 4 ) 将ILIMIT设置电阻从低侧MOSFET的漏极连接到ILIMIT，并使连接尽可能靠近芯片。从ILIMIT引脚到电阻的走线必须避免耦合到高压开关网。

- ( 5 ) 尽量减少从VCC和VIN引脚通过其各自的去耦电容器到GND引脚的回路面积。将这些电容尽可能靠近芯片。

## 4. Thermal Design and Layout

芯片有用工作温度范围受到以下因素的极大影响：功率MOSFET的平均栅极驱动电流要求；开关频率；工作输入电压（影响偏置稳压器LDO电压降，从而影响其功耗）；封装和工作环境的热特性。为了使PWM控制器在特定温度范围内有用，该封装必须允许有效地去除产生的热量，同时将结温保持在额定范围内。

CS5567E封装提供了一种通过封装底部暴露的热焊盘从半导体管芯中散热的方法。封装的暴露焊盘与芯片的基板（接地）热连接。这可以显著改善散热，因此PCB必须设计有热焊盘、热通孔和接地平面，以完成散热子系统。

CS5567E的暴露焊盘直接焊接到器件封装下方PCB上的接地铜焊盘上，将热阻降低到非常低的值。

从热焊盘连接到内部和焊料侧接地平面的许多直径为0.3mm的通孔对于帮助散热至关重要。在多层PCB设计中，实心接地平面通常放置在电源元件下方的PCB层上。这不仅为电源电流的流动提供了一个平面也代表了远离发热装置的导热路径。

MOSFET的热特性也很重要。高侧MOSFET的漏极焊盘通常连接到VIN平面以散热。低侧MOSFET的漏极焊盘连接到SW平面，但SW平面面积故意保持相对较小，以减轻EMI问题。

## 5. Ground Plane Design

如前所述，建议使用一个或多个内部PCB层作为固体接地平面。接地平面为敏感电路和走线提供屏蔽，并为控制电路提供安静的参考电位。使用暴露焊盘下的通孔阵列将PGND引脚连接到系统接地平面，还将PGND直接连接到输入和输出电容的返回端。PGND网络在开关频率处包含噪声，并且由于负载电流变化而可能反弹。PGND、VIN和SW的功率路径可以限制在接地平面的其中一侧，接地平面的另一侧包含的噪声要少得多，非常适合敏感的模拟信号走线。

上海智浦欣微电子有限公司

Chipstar Micro-electronics

CS5567E

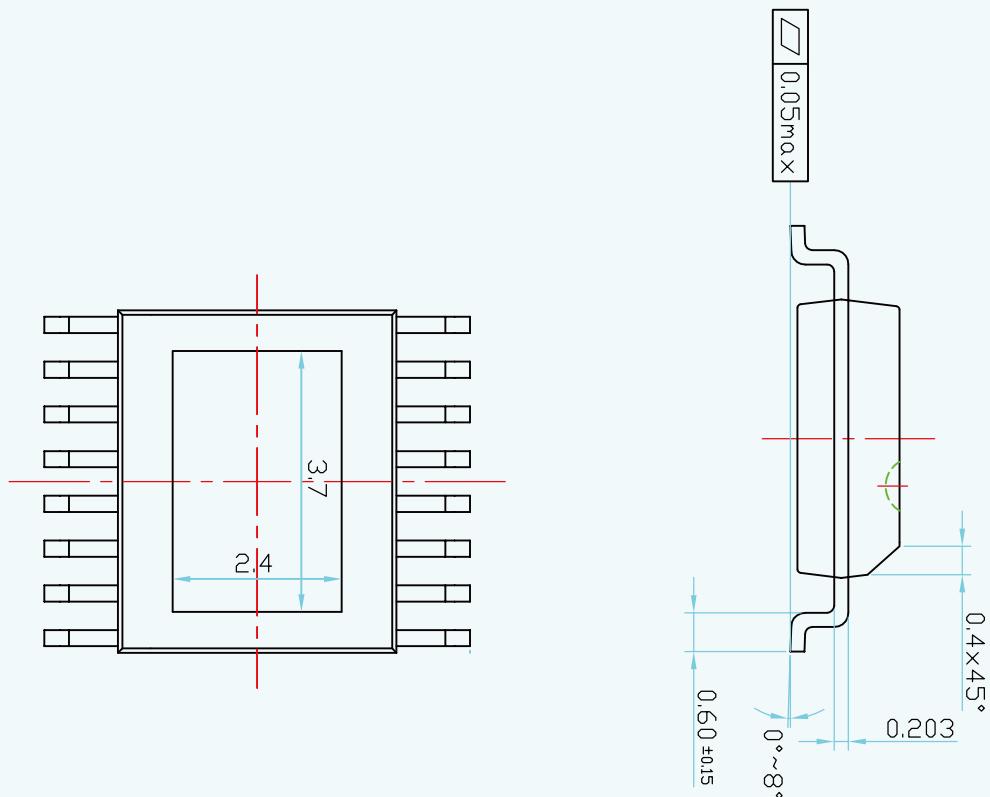

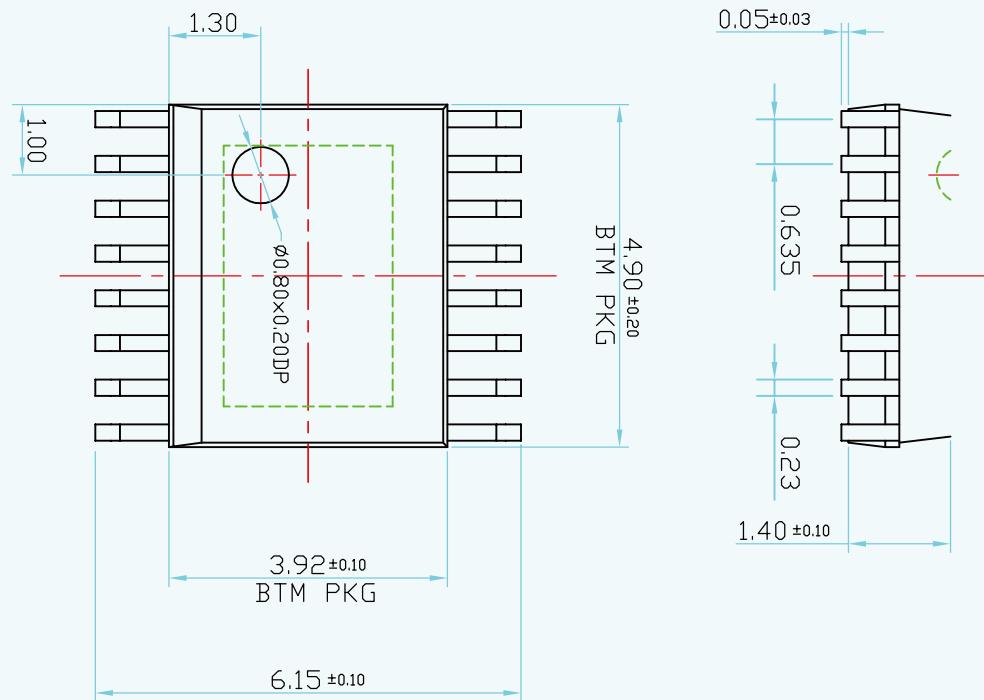

## 封装信息

CS5567E PACKAGE OUTLINE DIMENSIONS (units:mm)

## TAPE AND REEL INFORMATION

REEL DIMENSIONS

### MOS电路操作注意事项：

静电在很多地方都会产生，采取下面的预防措施，可以有效防止MOS电路由于受静电放电影响而引起的损坏：

- 操作人员要通过防静电腕带接地。

- 设备外壳必须接地。

- 装配过程中使用的工具必须接地。

- 必须采用导体包装或抗静电材料包装或运输。

### 声明：

- 上海智浦欣微电子有限公司保留说明书的更改权，恕不另行通知！客户在使用前应获取最新版本资料，并验证相关信息是否完整和最新。

- 任何半导体产品在特定条件下都有一定的失效或发生故障的可能，买方有责任在使用上海智浦欣微电子有限公司产品进行系统设计和整机制造时遵守安全标准并采取安全措施，以避免潜在失败风险可能造成人身伤害或财产损失情况的发生！

- 产品品质的提升永无止境，上海智浦欣微电子有限公司将竭诚为客户提供更优秀的产品！